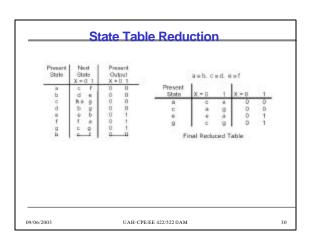

## **Implication Table Method**

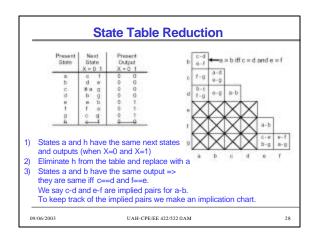

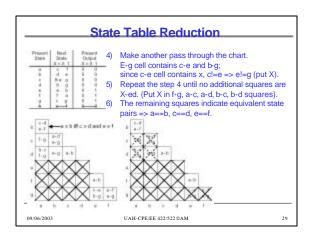

- 1. Construct a chart that contains a square for each pair of states.

- 2. Compare each pair in the state table. If the outputs associated with states i and j are different, place an X in square i-j to indicate that i!=j.

If outputs are the same, place the implied pairs in square i-j. If outputs and next states are the same (or i-j implies only itself), i==j.

- 3. Go through the implication table square by square. If square i-j contains the implied pair m-n, and square m-n contains X, then i!=j, and place X in square i-j.

- 4. If any Xs were added in step 3, repeat step 3 until no more Xs are added.

- 5. For each square i-j that does not contain an X, i==j.

UAH-CPE/EE 422/522 ©AM

09/06/2003

## Intro to VHDL

- · Technology trends

- 1 billion transistor chip running at 20 GHz in 2007

- Need for Hardware Description Languages – Systems become more complex

- Design at the gate and flip-flop level becomes

- very tedious and time consuming

- HDLs allow

- Design and debugging at a higher level before

- conversion to the gate and flip-flop level - Tools for synthesis do the conversion

- VHDL, Verilog

31

33

• VHDL - VHSIC Hardware Description Language

32

09/06/2003 UAH-CPE/EE 422/522 ©AM

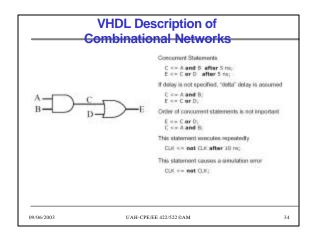

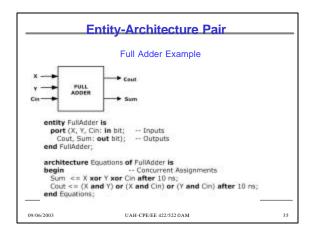

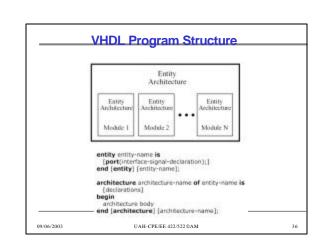

## Intro to VHDL Developed originally by DARPA – for specifying digital systems International IEEE standard (IEEE 1076-1993) Hardware Description, Simulation, Synthesis Provides a mechanism for digital design and reusable design documentation Support different description levels – Structural (specifying interconnections of the gates), – Dataflow (specifying logic equations), and – Behavioral (specifying behavior) Top-down, Technology Dependent

UAH-CPE/EE 422/522 ©AM

| 114  | t A B C | o C C1 | s s  | put | the |    | signals on the output list |

|------|---------|--------|------|-----|-----|----|----------------------------|

| Eor  | ce A 11 | 11     | 1.1  | set | the | A  | inputs to 1111             |

| for  | ce 8 00 | 01     |      | set | the | ъ  | inputs to 0001             |

| for  | ce Ci 1 |        |      | set | the | e: | to 1                       |

| 2.10 | 50      |        |      | run | the |    | inulation for 50 ns        |

| for  | ce Ci 0 |        |      |     |     |    |                            |

| for  | ce A 01 | 01     |      |     |     |    |                            |

| for  | ce B 11 | 10     |      |     |     |    |                            |

| 1.01 | 50      |        |      |     |     |    |                            |

| ne   | delts   |        | ь    | eo. | e   | ci |                            |

| D    | +0      | 0000   | 0000 | 0   | 000 | 0  | 0000                       |

| 0    | +1      | 1111   | 0001 | 0   | 000 | 1  | 0000                       |

| 10   | +0      | 1111   | 0001 |     | 001 |    | 1111                       |

| 20   | +0      | 1111   | 0001 | Ð   | 011 |    | 1301                       |

| 3.0  | +0      | 1111   | 0001 | 0   | 111 | 1  | 1001                       |

| 4.0  | +0.     | 1111   | 0001 |     | 111 |    | 0001                       |

| 50   | +0      | 0101   | 1110 | 1   | 111 | 0  | 0001                       |

| 60   | +0      | 0101   | 1110 | 1   | 110 | 0  | 0101                       |

| 70   | +0      | 0101   | 1110 | 1   | 100 | 0  | 0111                       |

| 60   | +0      | 0101   | 1110 |     | 100 | 0  | 0011                       |

| VHD                                                                                    | L Models for a l                                                                                                                        | NUX                                                                                    |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| NUX -                                                                                  | (not A and not B and 10)<br>(not A and B and 11) or<br>(A and not B and 12) or<br>(A and B and 13);<br>(X model using a conditional si) |                                                                                        |

| 1.6                                                                                    | F <= [0 when Sel = 0<br>else [1 when Sel = 1<br>else [2 when Sel = 2<br>else [3;                                                        | Sel represents the integer<br>equivalent of a 2-bit binary<br>number with bits A and B |

| If a MUX model is used insid<br>the MUX can be modeled us                              |                                                                                                                                         |                                                                                        |

| (cannot use a concurrent sta<br>case 5d is<br>when 0 => F <= 10;<br>when 1 => F <= 11; | the case statement has<br>case expression is<br>when choice?                                                                            | s the general form<br>=> sequential statements1<br>=> sequential statements2           |

| when 2 => F <= 12;<br>when 3 => F <= 13;<br>end case;                                  | T                                                                                                                                       | -> sequencial statements)                                                              |

| 09/06/2003                                                                             | UAH-CPE/EE 422/522 ©AM                                                                                                                  | 46                                                                                     |

|                                                                                                 | Models (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <pre>library IEEE;<br/>use IEEE.std_logic_unsigned.all;<br/>entity SELECTOR is<br/>port {</pre> | architecture RTL 1 of SELECTOR is<br>begin<br>p0 - process (A, SEL)<br>begin<br>if (SEL='0000') then $Y \ll A(0)$ ;<br>elsif (SEL='0001') then $Y \ll A(2)$ ;<br>elsif (SEL='0010') then $Y \ll A(2)$ ;<br>elsif (SEL='0011') then $Y \ll A(2)$ ;<br>elsif (SEL='0011') then $Y \ll A(2)$ ;<br>elsif (SEL='0101') then $Y \ll A(2)$ ;<br>elsif (SEL='1011') then $Y \ll A(2)$ ;<br>elsif (SEL='1011') then $Y \ll A(1)$ ;<br>elsif (SEL='1011') then $Y \iff A(1)$ ;<br>elsif (SEL='1011') then $Y \iff A(1)$ ;<br>elsif (SEL='1011') then $Y \iff A(1)$ ;<br>elsif (SEL='101') then $Y \iff A($ |  |

| MUX Models (2)                         |                                  |  |  |  |

|----------------------------------------|----------------------------------|--|--|--|

| library IEEE;                          | architecture RTL3 of SELECTOR is |  |  |  |

| use IEEE.std_logic_1164.all;           | begin                            |  |  |  |

| use IEEE.std_logic_unsigned.all;       | with SEL select                  |  |  |  |

| entity SELECTOR is                     | Y <= A(0) when "0000",           |  |  |  |

| port (                                 | A(1) when "0001",                |  |  |  |

| A : in std_logic_vector(15 downto 0);  | A(2) when "0010",                |  |  |  |

| SEL : in std_logic_vector(3 downto 0); | A(3) when "0011",                |  |  |  |

| Y : out std_logic);                    | A(4) when "0100",                |  |  |  |

| end SELECTOR;                          | A(5) when "0101",                |  |  |  |

|                                        | A(6) when "0110",                |  |  |  |

|                                        | A(7) when "0111",                |  |  |  |

|                                        | A(8) when "1000",                |  |  |  |

|                                        | A(9) when "1001",                |  |  |  |

|                                        | A(10) when "1010",               |  |  |  |

|                                        | A(11) when "1011",               |  |  |  |

|                                        | A(12) when "1100",               |  |  |  |

|                                        | A(13) when "1101",               |  |  |  |

|                                        | A(14) when "1110",               |  |  |  |

|                                        | A(15) when others;               |  |  |  |

|                                        | end RTL3;                        |  |  |  |

|                                                                                                                                                                                                                                                             | Vodels (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <pre>library IEEE;<br/>use IEEE act_logicn164.all;<br/>use IEEE act_logicunsigned.all;<br/>entity SELECTOR is<br/>port (<br/>A :in std_logic_vector(15 downto 0);<br/>SEL: in std_logic_vector(3 downto 0);<br/>Y : out std_logic);<br/>end SELECTOR;</pre> | architecture RTL20f SELECTOR is<br>begin<br>p1 : process (A, SEL)<br>begin<br>case SEL is<br>when '0000' => Y <= A(0);<br>when '0001' => Y <= A(2);<br>when '001' => Y <= A(2);<br>when '0101' => Y <= A(2);<br>when '0101' => Y <= A(3);<br>when '0101' => Y <= A(5);<br>when '0101' => Y <= A(5);<br>when '0101' => Y <= A(5);<br>when '0101' => Y <= A(6);<br>when '0101' => Y <= A(1);<br>when '1001' => Y <= A(1);<br>when '101' => Y <= A(1);<br>when '1101' => Y <= A(1);<br>when '1101' => Y <= A(1);<br>when '1101' => Y <= A(15);<br>when '1101' => Y <= A(15);<br>end case;<br>end Process; |  |

| 09/06/2003 UAH-CF                                                                                                                                                                                                                                           | PE/EE 422/522 ©AM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| MU                                                                                                                                                                                                                                       | MUX Models (4)         |    |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----|--|--|--|

| library IEEE;<br>use IEEE.std_logic_1164.all;<br>use IEEE.std_logic_unsigned.all;<br>entity SELECTOR is<br>port (<br>A : in std_logic_vector(15 downto 0)<br>SEL: in std_logic_vector(3 downto 0<br>Y : out std_logic);<br>end SELECTOR; |                        |    |  |  |  |

| 09/06/2003                                                                                                                                                                                                                               | UAH-CPE/EE 422/522 ©AM | 5( |  |  |  |